allegro如何导入原理图网表

我是小北,今天和大家一起来学习allegro如何导入原理图网表,下面小北讲解的内容是cadence生成网表并成功导入到PCB中。

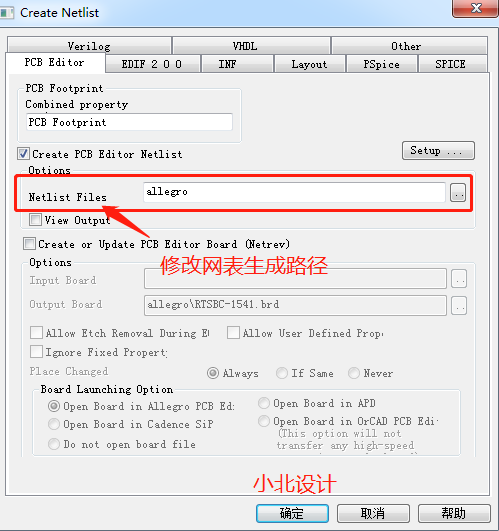

第一,我们打开orcad原理图软件。执行Tools>Create Netlist,弹出下面对话框。我们保持默认,不要修改任何参数。直接确定到底。会在原理文件夹中会生成一个”allegro”的文件夹。

我们也可以修改Netlist Files

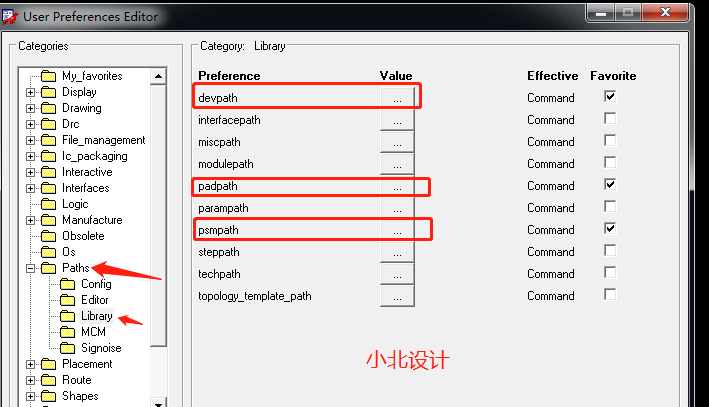

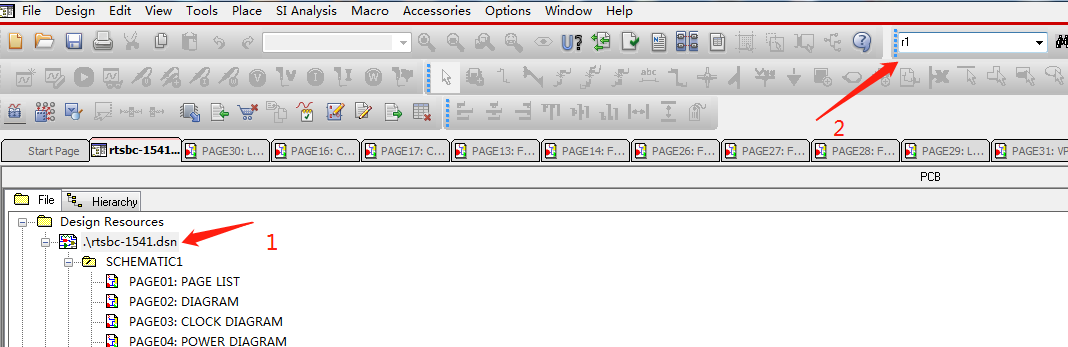

第二、打开allegro软件,我们设计一下库路径。执行Setup >User Preference,弹出User Preference Editor对话框,如下图所示 :我们在Paths > Library下面的devpath、padpath、psmath的路径修改为PCB封装库的路径。

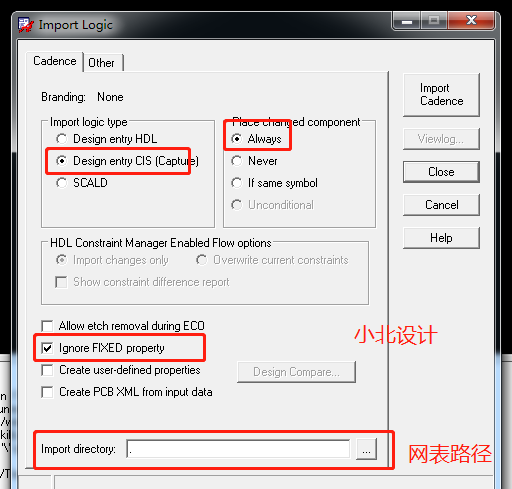

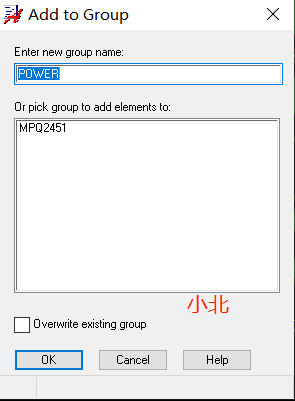

第三、在allegro PCB中改入原理图网表,执行File > Import >logic。弹出Import Logic对话框来,修改网表路径(Import directory),一般情况下,这个框口设置如下图所示:

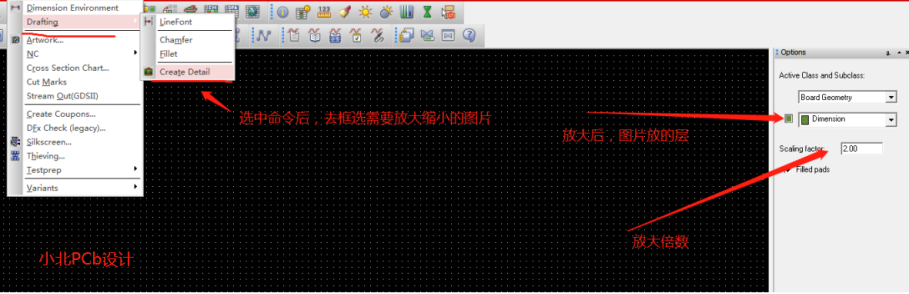

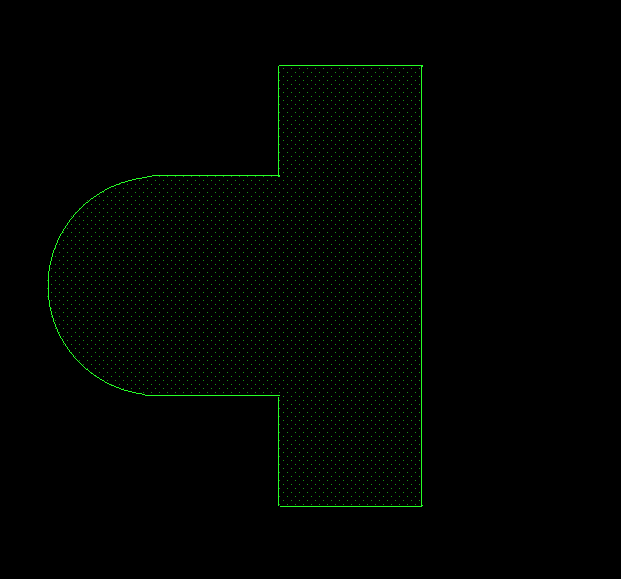

第四、绘制PCB板框。大家可以参考下小北写的allegro导入DXF。这个小北不详细的讲解了,我们直接在Board Geometry 中的Outime画一个边框。

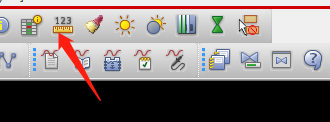

第五、放置元器件,执行Place >Quickplace,弹出Quickplace对话框,我们直接按place后,所有的器件将会摆放出来。然后点击OK后,再关闭对话框。

小北和大家allegro导原理图网表就到这里结束了,更多的设计技巧尽在小北设计

最新发布