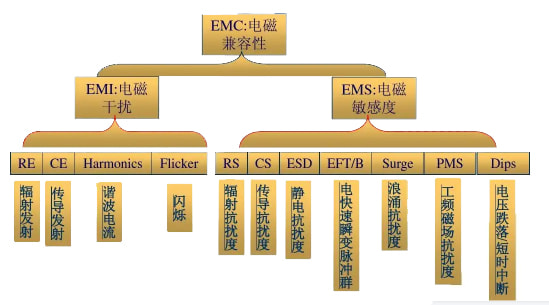

电磁兼容EMC、EMI简单的讲解及分析

电磁兼容学科主要研究的是如何使在同一电磁环境下工作的各种电气电子设备和元器件都能正常工作,互不干扰,达到兼容状态。

电磁兼容性EMC (Electromagnetic Compatibilty):设备在共同的电磁环境中能一起执行各自功能的共存状态,即该设备不会由于受到处于同一电磁环境中其他设备的电磁发射导致不允许的降级;也不会使同一电磁环境中其他设备因受其电磁发射而导致不允许的降级。

电磁干扰EMI (Electromagnetic Interference):指电磁骚扰导致电子设备相互影响,并引起不良后果的一种电磁现象。

其它几个小北今天几种电磁兼容就不多讲了。

电磁干扰三要素是电磁骚扰源、耦合途径(或称耦合通道)和敏感设备[23]。

电磁骚扰源指产生电磁骚扰的元件、器件、设备或自然现象;耦合途径(或称耦合通道)指把能量从骚扰源耦合到敏感设备上,并使该设备产生响应的媒介;敏感设备指对电磁骚扰产生响应的设备。所有的电磁干扰都是由上述三个因素组合而产生的。由电磁骚扰源发出的电磁能量,经过某种精合通道传输到敏感设备,导致敏感设备出现某种形式的响应并产生效果。

电磁兼容学科研究的主要内容是围绕构成电磁干扰的三要素进行的,即对电磁骚扰源、耦合通道和敏感设备的研究。骚扰源的研究包括具发生的机理、时域和频域的定量描述,以便从源端抑制干扰的发射,通常采用滤波技术来限制骚扰源的频谱宽度和幅值。

EMC的设计方法可以分为屏蔽隔离、滤波和接地。屏蔽隔离主要用于切断通过空间所前电耦合、做场感应耦合、电磁感应耦合形成的电磁噪声传播途径,这三种耦合义对应于静电尽蔽、磁场屏蔽与电磁屏蔽,衡量屏蔽的质量采用屏蔽效能这一指标;滤波是在频域上处理空磁噪声的一种技术,其特点是将不需要的一部分频谱滤掉;接地是提供有用信号或无用信号和心能吗声的公共涌路,接地的好坏直接影响到设各内部和外部的电磁兼容性

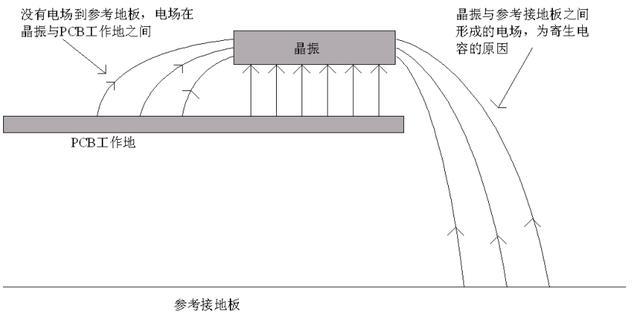

一、EMC屏蔽设计 屏蔽就是以金属隔离的原理来控制某一区域的电场或磁场对另一区域的干扰。它包括两个含义:一是将电路、电缆或整个系统的干扰源包围起来,防止电磁干扰向外扩散;二是用屏蔽体将接收电路、设备或系统包围起来,防止它们受到外界电磁干扰的影响。屏蔽按照机理可以分为电场屏蔽、磁场屏蔽、电磁场屏蔽三种不同方式。

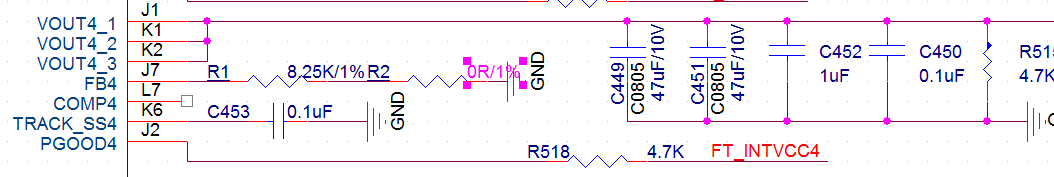

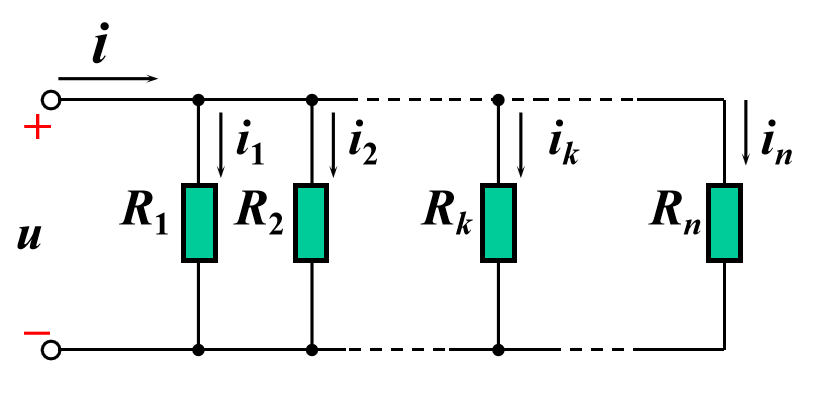

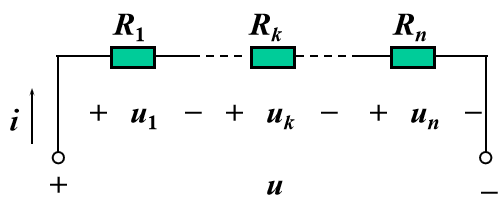

二、EMC滤波设计技巧 EMC设计中的滤波器通常指由L,C构成的低通滤波器。滤波器结构的选择是由"最大不匹配原则"决定的。即在任何滤波器中,电容两端存在高阻抗,电感两端存在低阻抗。

a. 电容值大小决定于电容的有效滤波频率,电容容值越大其滤波频率越低,反之亦然;

b. 电容容差一般无太多要求,一般在+/-20%;

一般分为三:+/-5%(J)、+/-10%(K)、+/-20%(M);

c. ESR(等效串联电阻)、ESL(等效串联电感)越小,滤波效果越好;d. 对于应用交流电源输入接口的对地Y电容,需要选择绝缘电阻较大的,一般按照安规要求大于20MΩ,有时还需要考虑Y电容的绝缘耐压值是否满足安规要求;

e. 如果较宽干扰频率的滤波电路,如电源电路和控制电路,需要采用不同容值电容进行搭配方式滤波,容差要有两个数量级;

f. 在电容的自谐振频率范围内,电容阻抗最小,滤波效果最佳。选择滤波电容时,电容的自谐振频率越接近干扰频率,滤波效果越好;

g. 针对三端电容和穿心电容,除了考虑电容正常参数外,还需要考虑两点:一是电容的通流量要满足电路的最大通流,且留一定余量;二是插入损耗在满足有用信号衰减情况下,插入损耗越大越好,插入损耗需要厂家给出;

h. 电容的额定电压大于电路工作电压;

电源电路:由于其工作频率非常低,故容值大小对电源电路工作无影响;

信号电路:

f﹤10MHz,信号线上允许加的电容值﹤1000pF;

10MHz ﹤f ﹤30MHz,信号线上允许加的电容值﹤100pF;

30MHz ﹤f ﹤50MHz,信号线上允许加的电容值﹤20pF;

50MHz ﹤f ﹤100MHz,信号线上允许加的电容值﹤10pF;

f﹥100MHz,需要谨慎使用电容。

三、EMC接地设计 接地是最有效的抑制骚扰源的方法,可解决50%的EMC问题。系统基准地与大地相连,可抑制电磁骚扰。外壳金属件直接接大地,还可以提供静电电荷的泄漏通路,防止静电积累。在地线设计中应注意以下几点:(1)正确选择单点接地与多点接地。在低频电路中,信号的工作频率小于1MHz,它的布线和器件间的电感影响较小,而接地电路形成的环流对干扰影响较大,因而应采用单点接地。当信号工作频率大于10MHz时,地线阻抗变得很大,此时应尽量降低地线阻抗,应采用就近多点接地。当工作频率在1~10MHz时,如果采用一点接地,其地线长度不应超过波长的1/20,否则应采用多点接地法。(2)将数字电路与模拟电路分开。电路板上既有高速逻辑电路,又有线性电路,应使它们尽量分开,而两者的地线不要相混,分别与电源端地线相连。要尽量加大线性电路的接地面积。(3)尽量增加接地线的连接。若接地线很细,接地电位则随电流的变化而变化,致使电子设备的定时信号电平不稳,抗噪声性能变坏。因此应将接地线尽量加粗,使它能通过它更它容易电流回流。如有可能,接地线的宽度应大于3mm。(4)将接地线构成闭环路。设计只由数字电路组成的印制电路板的地线系统时,将接地线做成闭环路可以明显提高抗噪声能力。其原因在于:印制电路板上有很多集成电路组件,尤其遇有耗电多的组件时,因受接地线粗细的限制,会在地结上产生较大的电位差,引起抗噪声能力下降,若将接地结构成环路,则会缩小电位差值,提高电子设备的抗噪声能力。

最新发布